# Low Power based Dynamic TSPC D flip flop for **High Performance Applications**

### Shruti Shrivastava, Usha Chauhan, Mohammad Rashid Ansari

Abstract: D flip-flop is viewed as the most basic memory cell in by far most of computerized circuits, which brings it broad usage, particularly under current conditions where high-thickness pipeline innovation is as often as possible utilized in advanced coordinated circuits and flip-flop modules are key segments. As a constant research center, various sorts of zero flip-flops have been concocted and explored, and the ongoing exploration pattern has gone to rapid low-control execution, which can be come down to low power-defer item. To actualize superior VLSI, picking the most proper D flip-flop has clearly become an incredibly huge part in the structure stream. The quick headway in semiconductor innovation made it practicable to coordinate entire electronic framework on a solitary chip. CMOS innovation is the most doable semiconductor innovation yet it neglects to proceed according to desires past and at 32nm innovation hub because of the short channel impacts. GNRFET is Graphene Nano Ribbon Field Effect Transistor, it is seen that GNRFET is a promising substitute for low force application for its better grasp over the channel. In this paper, an audit on Dynamic Flip Flop and GNRFET is introduced. The power is improved in the proposed circuit for the D flip flop TSPC.

Keywords: D Flip Flop, GNRFET, VLSI, Nano technology

# I. INTRODUCTION

As indicated by the past inquires about, some common D flip-flops with incredible execution have been introduced. As a common occurrence, the TSPC D flip flop proposed in [1] has significantly decreased the basic way delay and cleverly expelled the beat generator unit, which brings about an execution of semi static circuit and a particular preferred position as far as both speed and force scattering. In our work, MTSPC has been reinvestigated and changed as a key structure. From another perspective, with the innovation downsizing, spillage power dispersal has become an increasingly more significant piece of all out force scattering, and a few run of the mill new gadgets have been proposed to take care of this issue. Up until this point, GNRFET is by all accounts the most encouraging new gadget, and business chips have just been by significant foundries.

Revised Manuscript Received on June 30, 2020.

\* Correspondence Author

Shruti Shrivastava, M. Tech Scholar, Department of ECE, SEECE Galgotias University, Greater Noida, UP, India.E-mail: shrutishrivastavadec@gmail.com

Usha Chauhan, Department of ECE, SEECE Galgotias University, Greater Noida, UP, India. E-mail: usha.chauhan@galgotiasuniversity.edu.in Mohammad Rashid Ansari\* Department of ECE, SEECE, Galgotias University, Greater UP, E-mail: usha.chauhan@galgotiasuniversity.edu.in

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC BY-NC-ND license (<a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>)

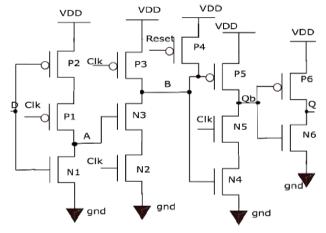

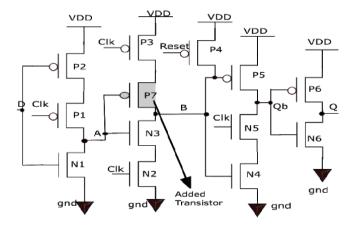

D Flip Flop is a significant classification of the successive circuit rationale family. It is utilized in practically all microchip and microcontroller chips and is a basic piece of the capacity and postponement giving contraptions and in Very Large Scale Integration ICs. In [1], a circuit is proposed which gives better execution in 180nm innovation and depends on the idea of TSPC which is famously known as pre-settable True Single Phase Clock based D flip f. This kind of D flip failure goes under the class of dynamic flip slumps and is regularly observed that its exhibition is obviously superior to that of the static D flip flop. Likewise, the traditional D flip flop dependent on TSPC have certain glitches included which are additionally overwhelmed by the utilization of adjusted TSPC based D flip failure. In the changed TSPC based D flip flop, an additional transistor is added to the way so that it smothers the flipping hubs and thus diminishes the glitches engaged with the circuit. [1].

Fig. 1: TSPC based D Flip Flop

Fig. 2: Modified TSPC based D Flip Flop

# Low Power based Dynamic TSPC D flip flop for High Performance Applications

The circuits viable for this exploration work are appeared in figure 1 and 2, as various glitches are found in TSPS D flip failure an altered form is likewise executed.

The regular D – Flip failure is the exceptionally essential plan of DFF. Hooks are regularly called level-touchy in light of the fact that their yield follows their contributions as long as they are empowered. They are dormant during this whole time when the empower signal is affirmed. There are circumstances when it is progressively valuable to have the yield change just at the rising or falling edge of the empower signal. This empower signal is generally the controlling clock signal. In this manner, we can have all progressions synchronized to the rising or falling edge of the clock. GNRFET has been acquainted with the plan of superior dynamic TSPC D flip-flops. In light of the fantastic electrical properties of GNRFET, the TSPC D flip-flop adjusted from unique TSPC by subbing SO-mode GNRFET for planar MOSFET has a huge decrease on power-defer item (PDP). Considering the special benefits of different working methods of GNRFET, further streamlining dependent on Modified TSPC dependent on MOSFET like GNRFET has been proposed to accomplish lower PDP and progressively productive territory usage rate. The reproduction results show that the Modified TSPC D Flip Flop decreases the PDP and somewhat expands the quantity of transistors.

#### II. LITERATURE SURVEY

- [1] Jahangir Shaikh (2018) et. PET requires significant standards, speedy and low force multichannel easy to mechanized converter (ADC).

- [2] M. Aguirre-Hernandez (2006) et. Al. In this paper, an investigation of past proposed clock gating plans for flip-flops was done, calling attention to the focal points and downsides displayed for each plan, as far as speed and force scattering. Some clock gating circuits were proposed and contrasted and existing ones, to decide the best performed one. So as to defeat the defer augmentation showed in past clock-gated edge-activated flip-flounders, clock-gating a heartbeat activated flip-flop was received and executed by utilizing the best performed check gating plan discovered Postponement and force demonstrated that the deferral was not influenced for our proposition and that the force decrease is more forceful for a pulse triggered flip-flop than for different plans.

- [3] MASSOUD PEDRAM (1996) et. Al Low force has risen as a chief subject in the present hardware industry. The requirement for low force has caused a significant change in outlook wherein power dispersal is as significant as execution and region.

- [4] Borivoje Nikolic (2008) et. Al. Innovation scaling has entered another period, where chip execution is compelled by power dissemination. Force limits shift with the application area; in any case, they direct the decisions of innovation and engineering and require execution procedures that exchange off execution for power reserve funds. This paper analyses innovation alternatives in the force restricted scaling system and surveys affectability-based examination that can be utilized for the ideal determination of ideal structures and circuit usage to accomplish the best execution under force limitations. These exchange off are analysed with regards to control minimization at the innovation, circuit, rationale, and engineering levels, both at the structure and run times. Today,

power restrictions are as significant in the plan just like the exhibition. Plan in the force restricted scaling system requires ceaseless changes in the models, circuit execution, and innovation decisions to augment the exhibition under force imperatives. Numerous procedures for bringing down force utilization are notable; however, their execution regularly acquires a presentation punishment. An ideal execution is accomplished when the vitality/postpone affectability of the plan is equivalent for all the structure and innovation factors. Execution of LP methods expands the plan and confirmation multifaceted nature and regularly requires unique innovation highlights, which builds the structure cost. Eventually, scaling will end when the expansion in the structure cost quits being reasonable.

- [5] Neil H. E. Weste (2007) et. Al in 1958, Jack Kilby constructed the principal coordinated circuit flip-flop with two transistors at Texas Instruments. In 2008, Intel's Itanium microchip contained in excess of 2 billion transistors and a 16 Gb Flash memory contained in excess of 4 billion transistors. [6] Surya Naik (2010) et. Al This paper identifies low force, rapid structure of flip-flop having less number of transistors and just a single transistor being timed by short heartbeat train which is genuine single stage timing (TSPC) flip-flop. Contrasted with Conventional flipflop, it has 5 Transistors and one transistor timed, in this manner has lesser size and lesser force utilization. It very well may be utilized in different applications like advanced VLSI timing framework, cushions, registers, microchips and so forth. TSPC Flip Flop is having less force utilization.

- [7] Betti A. (2011) et. Al creator explore the low-field phonon-constrained portability in easy chair graphene nanoribbons GNRs utilizing full-band electron and phonon scattering relations.

- [8] Satyendra Singh Chauhan (2013) et. Al Graphene nanoribbons (GNRs) are required to show unprecedented properties as nanostructures. The impact of boron and nitrogen substitutional doping at four progressive situations on electronic and transport properties of crisscross graphene nanoribbons (ZGNRs) is examined utilizing turn unpolarized thickness useful hypothesis.

- [9] Anantha P. Chandrakasan (1992) et. Al Motivated by rising battery-worked applications that request serious calculation in versatile situations, strategies are explored which lessen power utilization in CMOS advanced circuits while keeping up computational throughput. Methods for low-power activity are indicated which utilize the most reduced conceivable gracefully voltage combined with building. rationale style, circuit. and innovation improvements. A structural based scaling technique is introduced which shows that the ideal voltage is a lot of lower than that controlled by other scaling contemplations. This ideal is accomplished by exchanging expanded silicon zone for diminished force utilization. There are an assortment of contemplations that must be considered in low-power structure which incorporate the style of rationale, the innovation utilized, and the rationale executed. Variables that were appeared to add to control dissemination included false advances because of dangers and basic race conditions, spillage and direct way flows, precharge advances,

and force devouring advances in unused hardware. A pass-entryway rationale family with changed edge voltages was seen as the best entertainer for low-power plans,

because of the insignificant number of transistors required to execute the significant rationale capacities. An investigation of transistor estimating has indicated that base measured transistors ought to be utilized if the parasitic capacitances are not exactly the dynamic entryway capacitances in a course of rationale doors.

[10] Scott Chilstedt (2010) et. Al Throughout a significant part of the semiconductor business' history, the advanced transistor kept up a recognizable metal-oxide-semiconductor (MOS) structure utilizing a polycrystalline silicon door, a silicon dioxide encasing, and a solitary gem silicon channel. Be that as it may, proceeded with innovation scaling brings various new plan issues, and elective structures are getting favourable. As of late, high-K dielectrics and metal doors have seen across the board appropriation to battle rising spillage power utilization. To continue scaling later on, options in contrast to the regular silicon channel should likewise be thought.

[11] Huei Chaeng Chin (2014)et.al Enhanced Device and Circuit-Level Performance Benchmarking of Graphene Nano-ribbon Field-Effect Transistor against a Nano-MOSFET with Interconnects Graphene nano-ribbon field-influence transistor (GNRFET) and a nano scale metal-oxide semiconductor field-influence transistor (nano-MOSFET) for applications in ultra-titanic scale joining (ULSI) is appeared.

[12] Amit Sanga (2016) et.al GNRFET as future low force contraptions — the graphene nano-ribbon field influence transistor (GNRFET) is a making advancement that gotten a lot of thought beginning late. Late work on GNRFET circuit re-institutions has indicated that GNRFETs may have potential in low force applications.

[13] Wan Sik Hwang (2013) In spite of earlier impression of jumbled vehicle and absurd edge-ruthlessness impacts of GNRs, the exploratory outcomes presented here undeniably show that the vehicle instrument in deliberately made GNRFETs is standard band-transport at room temperature, and between band burrowing at low temperature.

[14] Youngki Yoon (2008) et.al We present an atomistic 3D re-establishment take a gander at of the general execution of graphene nano-ribbon (GNR) Schottky hindrance (SB) FETs and transistors with doped stores (MOSFETs) by utilizing oneself steadfast answer of the Poisson and Schrödinger conditions inside the non-understanding green's trademark (NEGF) formalism. Immaculate MOSFETs show scarcely higher electrical execution, for each virtual and THz applications. The impact of non-idealities on mechanical gathering when everything is said in done execution has been examined, considering the closeness of single void, a territory brutality and ionized defilements close to the channel. All around, MOSFETs demonstrate additional solid properties than SBFETs.

[15] Mayank Mishra (2017) et.al Performance improvement of GNRFET Inverter at 32nm development place point Moore's standard has been a vital benchmark for movements inside the district of microelectronics and data dealing with. Believe it or not, it has played an instrumental situation in driving the field budgetary issues and dividing down of the trademark timespan has been the central system for improving the general execution of the contraption.

[16] DEVENDRA UPADHYAY (2015) et.al Understanding the impact of graphene sheet fitting on the conductance of GNRFETs The impact of fitting the graphene sheets used as redirect in a graphene nano-ribbon field influence transistor (GNRFET) was researched.

[17] Maedeh Akbari Eshkalak (2014) et.al Used Graphene nano-ribbon Field influence transistor with 2 door encasings. Right now door separators are offered in graphene field influence transistor which adds to the advantage of low and high dielectric constants.

[18] Nima Dehdashti Akhavan (2011) et.al Study of dependably doped graphene nano-ribbon transistor (GNR) FET utilizing quantum proliferation. Right now, watch the general execution of dependably doped graphene nano-ribbon FET (GNRFET). 3-dimensional quantum mechanical augmentations based at the NEGF formalism had been used inside observing electron-phonon trade to analyse the general execution of GNRFET. We saw out that dependably doped GNRFET will manufacture the flexibility and execution of GNRFET device stand out from for the most part undoped graphene.

[19] Mihir R. Choudhury (2008) et.al (GNRFETs) are promising contraptions for past CMOS nano gadgets because of their mind-blowing transporter transport properties and potential for huge scope dealing with and creation. This paper joins atomistic quantum-transport displaying with circuit re-sanctioning to perform advancement assessment for GNRFET circuits.

[20] Seyed Saleh Ghoreishi (2017) et.al In this paper, a burrowing graphene nano ribbon field influence transistor with electrically instituted channel development, to be express, EA-T-GNRFET, is proposed. The proposed structure consolidates a side door at the channel side with a dependable voltage and length of 0.4 V and 15 nm, independently.

[21] M. Arunlakshman (2014) et.al The observed Moore's law conveys that —For reliably and a huge bit of the degree of transistors which may be to be melded on a kick the holder gets increased indefinitely. consequently, the there exists a method implied as the scaling. MOSFET is one of the extraordinary transistors utilized in contemporary devices. The most discouraged piece of the MOSFET is that it can't be reduced underneath 10nm considering the manner in which that it impacts in the short channel results, wherein the channel an area between the source and the channel would be not prepared to lead charmingly, passed on to it, significance and speed additionally plays out a fundamental situation inside the VLSI development. For and structure the criticalness affirmation should be especially less and pace of should be to an additional volume. To beat this issues, another out of the plastic new transistor to substitution MOSFET for destiny gear should be researched to get higher outcomes in verbalizations of all the enormous show parameters like force, locale and pace.

[22] Wan Sik Hwang (2015) et al., We report the attestation of top-gated graphene nano-ribbon field influence transistors (GNRFETs) of  $\sim \! 10$  nm width on immense zone epitaxial graphene demonstrating the opening of a band hole of  $\sim \! 0.14$  eV.

# Low Power based Dynamic TSPC D flip flop for High Performance Applications

[23] M.M Anas (2015) et al, A victor among the most important highlights of graphene Nano ribbons, from both head science and application perspectives, is their electrical band hole. Right now, consider the legitimacy of band opening in single and twofold layer Graphene nano ribbons (GNRs) of decided widths and edge geometries. The figuring's are finished utilizing Tight Binding quantum mechanical spreads for verifying the overhauled nuclear courses of action of the nano-ribbons and their electronic structures. Our estimations show that for single-layer graphene nano-ribbon with a width of 12A0, the one with rocker edge is semiconducting with a band hole of 0.25 eV while the one with screw up edge is metallic. For bilayer nano-ribbons, two specific stacking structures (AA and AB) are considered.

#### III. PROPOSED WORK

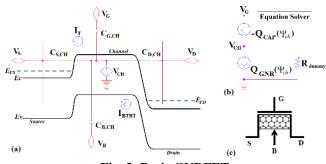

Some of the field-effect transistors use the carbon-based Nano-materials which are reviled by encouraging the new next-generation electrical appliances because of their excellent and improved electrical properties and integration capabilities through new fabrication techniques. The two most commonly studied are carbon nanotube FETs (CNFETs) and graphene Nano ribbon FETs (GNRFETs). Compared to cylindrical CNTs, GNRs can be grown through a silicon compatible, transfer-free, and in situ process, thus facing some of the nonalignment and a little bit of transfer-related problems as compared or interfaced by circuits based on CNT. A graphene Nano ribbon Field-Effect Transistor which is also known as GNRFET refers to a transistor of kind field-effect transistor which will use a very normal single sheet of graphene or an collection of graphene sheets as the material of its channel beside using a bulk silicon in the traditional MOSFET structure.

Fig. 3: Basic GNRFET

The atomic structure is the basic building block of any structure so it is the basic block of Graphene which provides us to use it in its exceptional electrical, optical, mechanical and thermal properties. Generally, the most innovating and fascinating electrical properties are high mobility of a particular electron and ballistic transport of charge carriers. But at the same point all these properties have a little bit of twist in them that twist was; Graphene is a type of semiconductor which will have a zero-band gap, or also can be termed as semimetal. Basically, the decrement or shortage of band gap in some intrinsic type of Graphene is a perhaps, together with a very large-scale manufacturing, this was the most difficult engineering problem. If there is a zero-band gap of any semiconductor then this will mean that Graphene cannot switch its state from the conductive state to the

non-conductive state. Only when externally some conditions are applied on it then it will change its non-conducting state and comes in the conducting state.

If the material of Graphene is such that it is structured as a basic Nano ribbons, then using the normal planar new technologies some of the new technologies are electron beam lithography and etching, a sizeable band gap opens.

In this methodology, firstly the circuits are designed using coding approach HSPICE, then the circuit are testes using Avanwaves and compared using the performance metrics. The circuit under implementation is given below in fig. 1 and fig 2. The circuit can be implemented on various types of GNRFET configurations.

#### IV. RESULT AND DISCUSSION

This section shows the existing results of paper [1]. Here it is seen that the power is better in modified TSPC configuration and few other parameters like delay and frequency are taken into consideration.

The results are presented in table 1 shown below:

Table 1: Results for TSPC and Modified TSPC based dynamic D Flip Flop

| ajname 2 i np i top                |           |           |  |

|------------------------------------|-----------|-----------|--|

| Performance<br>parameters          | TSPC DFF  | MTSPC DFF |  |

| Input clock frequency              | 1 GHz     | 1 GHz     |  |

| Clock-to-Q delay (Low-<br>to-High) | 92.95 ps  | 61.08 ps  |  |

| Clock-to-Q delay (High-<br>to Low) | 143.6 ps  | 122.9 ps  |  |

| Average Clock-to-Q<br>delay        | 118.27 ps | 91.99 ps  |  |

| Setup time(t <sub>setup</sub> )    | 70.13 ps  | 64.14 ps  |  |

| Hold time(t <sub>bet6</sub> )      | ≈ 0       | ≈ 0       |  |

| Average power consumption          | 75.43 μW  | 21.83 μW  |  |

Table 2: Results for Power Consumption and Power Delay Product

| Delay 1 Toduct                      |                                |                                 |  |

|-------------------------------------|--------------------------------|---------------------------------|--|

| Performance<br>parameter            | TSPC DFF based<br>gray counter | MTSPC DFF based<br>gray counter |  |

| Maximum frequency of<br>operation   | 500 MHz                        | 1 GHz                           |  |

| Maximum propagation<br>delay of MSB | 1.6 ns                         | 0.96 ns                         |  |

| Power consumption                   | 1.52 mW<br>(1.52×E-3)          | 244.2 μW<br>(244.2×E-6)         |  |

| Power Delay<br>Product(PDP)         | 2.4 pJ<br>(2.4×E-12)           | 0.23 pJ<br>(0.23×E-12)          |  |

In table 2 above, the results are further concluded for the TSPC and Modified TSPC based gray counter as implemented in [1].

#### V. CONCLUSION

In this work two D Flip-Flop one using TSPC i.e. presetable true single phase clock based D flip flop and a modified version which consists of an extra transitory to reduce power consumption are researched in various technology to improve their power and speed.

Also an expected comparative study for various performance parameters like Average power, delay can be presented in future work. It is expected to see in results that the GNRFET technology can effectively reduce power and delay of logic flip flop and gates.

#### **REFERENCES**

- Jahangir Shaikh, Hafizur Rahaman, "High speed and low power preset-able modified TSPC D flip-flop design and performance comparison with TSPC D flip-flop", IEEE, 2018

- M. A. Hernandez and M. L. Aranda, "A Clock Gated Pulse-Triggered D Flip-Flop for Low Power High Performance VLSI Synchronous Systems," Proceedings of the 6thInternational Caribbean Conference on Devices, Circuits and Systems, Mexico, pp. 293-29, 28 April 2006.

- M. Pedram, "Power minimization in IC Design: Principles and applications," ACM Transactions on Design Automation of Electronic Systems, Vol. 1, No. 1, January 1996

- B. Nikolic, "Design in The Power Limited Scaling Regime," IEEE Transaction on Electronic Devices, Vol. 55, No. 1, pp. 71-83, January 2008.

- Neil H. E. Weste, David Harris, Ayan Banerjee, "CMOS VLSI DESIGN: A Circuits and Systems Perspective", Third Edition, 2007.

- Surya Naik and Rajeevan Chandel, "Design of a Low Power Flip-Flop Using CMOS Deep Submicron Technology", IEEE International Conference on Recent Trends in Information, Telecommunication and Computing (ITC), pp. 253-256, 2010

- Betti A., Fiori G., and Iannaccone G (2011).," Strong mobility degradation in ideal graphene nanoribbons due to phonon scattering,", volume-98, issue 21, Appl. Phys Lett., 2011.

- 8. Chauhan S.S. et al (2012)," Band gap engineering in zigzag graphene nano ribbons anab initio approach," Journal of Computational and Theoretical Nanoscience Volume 9, Number 8 (August 2012) pp.1023-1133.

- Chandrakasan A.P. Sheng S. Brodersen R.W (1992).: "Low-power CMOS digital design", IEEE Journal of Solid-State Circuits, Volume 27, Issue4, April 1992 Page(s):473 – 484.

- Chilstedt S., Dong C., and Chen D (2010).," Carbon nanomaterials transistors and circuits, transistors: Types, materials and applications," Nova Science Publishers, 2010.

- Chin, Huei& Lim, Cheng Siong& Soon Wong, Weng& A. Danapalasingam, Kumeresan& K. Arora, Vijay & Tan, Michael. (2014). Enhanced Device and Circuit-Level Performance Benchmarking of Graphene Nano-ribbon Field-Effect Transistor against a Nano-MOSFET with Interconnects. Journal of Nanomaterials, 2014. 1-14. 10.1155/2014/879813.

- Sanga, MohammadiBanadaki, Yaser& Srivastava, A &Sharifi, Safura. (2016). Graphene nano-ribbon field effect transistor for nanometer-size on-chip temperature sensor. 980203. 10.1117/12.2219346.

- 13. Hwang, Wansik& Zhao, Pei & Tahy, Kristof & O. Nyakiti, Luke & D. Wheeler, Virginia & L. Myers-Ward, Rachael & R. Eddy Jr, Charles & Kurt Gaskill, D & Robinson, Joshua & Haensch, Wilfried& An, Huili&, Xing & Seabaugh, Alan & Jena, Debdeep. (2013). Graphene Nano-ribbon Field-Effect Transistors on Wafer-Scale Epitaxial Graphene on SiC substrates. APL Materials. 3, 10.1063/1.4905155.

- Yoon, Youngki& Fiori, Gianluca& Hong, Seokmin&Iannaccone, Giuseppe &Guo, Jing. (2008). Performance Comparison of Graphene Nano-ribbon FETs With Schottky Contacts and Doped Reservoirs. IEEE Transactions on Electron Devices, 55. 10.1109/TED.2008.928021.

- Mayank Mishra, RonilStieven Singh ,Ale Imran "Performance optimization of GNRFET Inverter at 32nm technology node", materials today proceeding, Volume 4, Issue 9, 2017, Pages 10607-10611

- 16. DEVENDRA UPADHYAY and SUDHANSHU CHOUDHARY "Understanding the impact of graphene sheet tailoring on the conductance of GNRFETs", Bull. Mater. Sci., Vol. 38, No. 7, December 2015, pp. 1705–1709.c@Indian Academy of Sciences.

- 17. Maedeh Akbari Eshkalaka,n, Rahim Faezb, Saeed Haji-Nasiria "A novel graphene nano-ribbonfield effect transistor with two differentgate insulators" http://dx.doi.org/10.1016/j.physe.2014.10.0211386-9477/&2014 Elsevier

- DehdashtiAkhavan, Nima&Ferain, Isabelle & Yu, Ran &Razavi, Pedram&Colinge, Jean-Pierre. (2012). Influence of discrete dopant on

- quantum transport in silicon nanowire transistors. Solid State Electronics. 70. 92-100. 10.1016/j.sse.2011.11.017.

- Choudhury, Mihir& Yoon, Youngki&Guo, Jing &Mohanram, Kartik.

(2008). Technology exploration for graphene nano-ribbon FETs.

272-277. 10.1145/1391469.1391539.

- Yousefi, Reza &Ghoreishi, Seyed. (2017). A computational study of a novel graphene nano-ribbon field effect transistor Read More: http://www.worldscientific.com/doi/abs/10.1142/S021797921750056

4?src=recsys. International Journal of Modern Physics B. 10.1142/S0217979217500564.

- [21] M.Arunlakshman "Effect of 15nm Graphene Nano Ribbon Field Effect Transistors(GNRFET)on Single Edge Triggered D –Flip Flop based Shift Registers and its comparison with 16nm MOSFET Technology", International Journal of Emerging Technology and Advanced Engineering Website: www.ijetae.com(ISSN 2250-2459,ISO 9001:2008Certified Journal,Volume 4, Issue 4,April2014),

- Wan Sik Hwang1,2,b), Pei Zhao1, Kristof Tahy1, Luke O. Nyakiti3,4, Virginia D. Wheeler3, Rachael L. Myers-Ward3, Charles R. Eddy Jr.3, D. Kurt Gaskill3, Joshua A. Robinson5, Wilfried Haensch6, Huili (Grace) Xing1, Alan Seabaugh1, and Debdeep Jena1,b)"Graphene nano-ribbon field-effect transistors on wafer-scale epitaxial graphene on SiC substrates" APL Materials 3, 011101 (2015); https://doi.org/10.1063/1.4905155

- M. M. Anas, "A Study of Single Layer and Bilayer GNRFET," 2016 UKSim-AMSS 18th International Conference on Computer Modelling and Simulation (UKSim), Cambridge, 2016, pp.93-96.doi: 10.1109/UKSim.2016.50

#### **AUTHORS PROFILE**

**Shruti Shrivastava** is pursuing her M.Tech.(VLSI Design) degree from Galgotias University, Greater Noida, UP, India. Her area of interest includes VLSI design and research area is GNRFET (Graphene Nano Ribbon Field Effect Transistor)

**Dr Usha Chauhan** is a Associate Professor at the School of Electrical, Electronics and Communication Engg. Galgotias University. She received her B. Tech (Electronics and Communication Engg) in 1999, from government college UBDTCE Karnataka, a M. tech in 2007, and a Ph.D (Electronics and Communication Engg) in 2018, from Bhaghwant University AJMER.

Her research interests are image processing, computer vision and Embedded System.

**Dr. Mohammad Rashid Ansari**, has earned his B.Tech., from, AMU, Aligarh in 2001, M.Tech. (Digital Systems), from MNNIT, Allahabad, in the year 2003 and completed his Ph.D. from Jamia Millia Islamia (A Central University) in 2019.

He is currently working as Faculty member in Department of ECE in SEECE, Galgotias University.

He is having more than seventeen years of teaching and research experience. Besides organizing national and international workshops and conferences, he has published several research papers in various International Journals and International/National conferences, has also attended several national and international conferences and workshops. His areas of interest include Network-on-Chip, Digital Signal Processing and Image Processing. He was technical committee members of many international conferences, including ICEEE2020, RDCAPE2019, NANOfIM2017, GUCON 2019. He has received best paper award in INDICON 2015. He is a member of IEEE.