# Consequences of Body-Biasing Technique on **SRAM Memory**

Mukesh kumar, J.S. Ubhi

Abstract: The circuit changes the threshold voltage effectively with a definite delay and power by altering the body biasing of the transistors. The body bias is employed to govern the frequency and leakage of the memory device. The threshold voltage of individual transistor is decreases by applying the reverse body bias (RBB) and increases with forward body bias (FBB). This paper presents the viability of RBB to decrease the leakage power and increase in the speed of operations for SRAM circuit. The investigation of RBB dependencies on various performance parameters are analyzed. It is observed that the leakage power improves by 30.32% on applying RBB voltage compared to zero body bias while the transient power increases by 3.22% but decrease of delay by 84.56% dominates on it. Because of this the overall energy consumption reduces by 84.06%. Further the simulation work is carried out to see effect of supply voltage variation on leakage power at different RBB voltage and temperature. Therefore, the RBB scheme is beneficial for devices of low leakage, low energy and high speed of operation but this RBB voltage is limited by band-to-band tunneling current.

Index terms: RBB, Frequency, leakage power, delay

#### I. INTRODUCTION

Through persistent scaling in CMOS technology, the feature size of the incorporated circuits encounters numerous physical confinements. The increasing leakage current, and the number of transistor per unit area leads to power dissipation in the device. Numerous applications like analog to digital converter, cache memory of computer, laptop, high speed registers, electronic toys, biomedical and wireless sensor networks, need very low-power circuits for long-time performance [1, 2]. The power dissipation, stability and operating frequency are the main concern in semiconductor industry. The device performance deterioration is because of bias temperature instability (BTI), hot carrier injection (HCI), time-dependent dielectric breakdown (TDDB), etc. that causes irregular functioning, unsuitable biasing inappropriate environment condition during their working [3]. The substrate or body of MOS devices in a design is common, therefore body of all often kept at same voltage. The body biasing technique is utilized to alter the threshold voltage of transistors. As the source to body bias voltage increases, the depletion width of channel-body increases resulting in enhanced trapped charge density in depletion region and to maintain neutrality in channel charge must

Manuscript published on 30 August 2019.

\*Correspondence Author(s)

Mukesh Kumar, Department of ECE, Sant Longowal Institute of Engineering and Technology, Longowal, Sangrur, India.

Corresponding author: mukeshrai131985@gmail.com

Dr. J. S. Ubhi, Department of ECE, Sant Longowal Institute of Engineering and Technology, Longowal, Sangrur, India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license http://creativecommons.org/licenses/by-nc-nd/4.0/

decrease. It impacts on the gate channel potential drop by adding of body bias to the channel-body junction voltage [4]. Various schemes have been implemented to apply body biasing on the transistors to decrease the delay (by reducing threshold voltage), the active power (on bringing down supply as well as threshold voltages although keeping up a similar speed when compared with a high threshold voltage circuit), leakage current or intra-die as well as inter-die threshold voltage disparity (by adaptive biasing) [5, 6]. The power and current requirement of body bias generator may get important, if the body bias voltage of transistors of a circuit is adjusted [7]. There may be two types of body biasing implemented: FBB is used to reduce threshold voltage and enhance device performance while RBB is utilized to enhance the threshold voltage and reduce the leakage current and hence power [8]. The use of the FBB is to boost threshold voltage roll-off conduct empowers the utilization of shorter gates can be clarified by a quasi 2-Dimensional model. RBB technique is often used to reduce the leakage of the circuit especially when it becomes idle. Reverse body biasing leads to increase in threshold voltage and hence decreasing the subthreshold leakage current. However, band to band tunneling current from source to substrate and drain to substrate p-n junction diode increases with increase of reverse bias voltage [9]. It is approaching to reduced leakage current at high value of reverse bias voltage. Consequently, an optimum RBB voltage is restricted by increased band-to-band tunneling currents that can be used in a transistor to decrease the total leakage current [10]. The efficacy of RBB is diminished as scaling of technology occurs because of increased effect of short channel and reduced impact of body effect [5], [9]. It is assumed that forward body biasing approach may be an alternate to the reverse biasing. It not only increases the body effect but also reduces the short channel effect. It is supposed that forward body biasing will be more productive in managing the threshold voltage of MOS device in near future technology as the ratio of supply voltage to threshold voltage reduces with scaling of technology [7]. The reverse body biasing voltage of a MOS transistor is limited by the voltage applied across the gate oxide. It can also be decreased by scaling down the gate oxide thickness in future generation of technology [11]. The remaining of the paper is structured as the following: In section II, the proposed SRAM cell structure is described. Section III shows the simulation results of the performance parameters by applying the body biasing of the SRAM cell. Finally, Section IV includes the conclusion and at last references are included.

Retrieval Number: I8637078919/19©BEIESP DOI: 10.35940/ijitee.I8637.0881019 Journal Website: www.ijitee.org

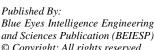

## II. SCHEMATIC OF PROPOSED 10T SRAM MEMORY CELL

The transistor gating (TG) technique is utilized in design of a 10T SRAM cell from 6T SRAM cell and schematic is displayed in the Fig.1. It has transistor PM2 in the middle of PM0 & QB while PM3 is connected among PM1 & Q. NM2 transistor follows among NM1 & ground though NM3 is associated among NM0 & ground. Transistor PM3 is connected among PM1 & Q though NM2 in the middle of NM1 and ground. The transistors PM2 & PM3 are connected at draw up segment while NM2 & NM3 is associated to draw down part. Sleep transistors are "turned on" in active mode with the use of suitable gate voltage & stays "off" for hold condition on admissible gate supply voltage.

Fig.1 Schematic of 10T SRAM cell

## III. RESULTS AND DISCUSSION

The threshold voltage of the transistor is demonstrated as a function of substrate bias co-efficient (Y), fermi-level ( $\phi_F$ ) and source to body bias voltage  $(V_{SB})$  as shown in equation given below [4]

$$V_{T} = V_{T0} + \gamma \left( \sqrt{\left| -2 \phi_{F} + V_{SB} \right|} - \sqrt{\left| 2 \phi_{F} \right|} \right)$$

(1)

$$\gamma = \sqrt{2q \, N_A \in_{Si}} / C_{OX} \tag{2}$$

$$C_{OX = \in S_i/t_{ox}} \tag{3}$$

$$\phi F = \frac{KT}{q} \ln \left( \frac{n_i}{N_A} \right)$$

(4)

The variable  $V_{TO}$ , q,  $N_A$ ,  $C_{Si}$ ,  $t_{ox}$ ,  $C_{ox}$ , K, T,  $n_i$  represent the threshold voltage when source to body is at zero potential, charge of carriers, acceptor concentration, permittivity of Si, oxide layer thickness, oxide capacitance, Boltzmann constant, temperature in kelvin and intrinsic Si concentration respectively.

### Forward body biasing of NMOS

By keeping PMOS to maximum supply voltage and increasing NMOS body voltage above ground level is forward biasing condition. The simulation result is shown in the Table.1 as shown below

Table 1 Forward body biasing simulation results of

| NMOS 10T SRAM memory cell.   |                            |                      |           |  |

|------------------------------|----------------------------|----------------------|-----------|--|

| Forward Biasing<br>voltage   | Transient<br>power<br>(nW) | Static power<br>(pW) | Delay(ps) |  |

| $V_{PB} = 1V, V_{NB} = 0V$   | 353.59                     | 3.40                 | 814.12    |  |

| $V_{PB} = 1V, V_{NB} = 0.2V$ | 352.45                     | 6.04                 | 851.98    |  |

| $V_{PB} = 1V, V_{NB} = 0.4V$ | 352.08                     | 26.35                | 879.46    |  |

| $V_{PB} = 1V, V_{NB} = 0.6V$ | 379.68                     | 327.42 (n)           | 898.83    |  |

| $V_{PB} = 1V, V_{NB} = 0.8V$ | 41.26 (µ)                  | 42.03 (μ)            | 912.08    |  |

| $V_{PB} = 1V, V_{NB} = 1V$   | 9.93 (m)                   | 10.15 (m)            | 922.25    |  |

The forward body biasing simulation results shows that the transient power, leakage power and delay of SRAM memory cells increase with increase of forward body biased condition. The transient and leakage power increases by large amount as the biasing voltage increases after 0.6 V.

The threshold voltage variation of access transistors NM4 and NM5 of 10T SRAM as shown in Fig.1, with forward biasing and reverse biasing is illustrated in Fig.2. The threshold voltage decreases with forward biasing and increases with reverse biasing the body of NMOS transistor of SRAM memory. With FBB the threshold voltage of NM4

■ Threshold voltage (of NM4) ■ Threshold voltage (of NM5)

|             | 1    | 621.958 | 508.138 |

|-------------|------|---------|---------|

| 5           | 0.8  | 647.46  | 515.92  |

| voltage (V) | 0.6  | 671.08  | 530.01  |

| tag         | 0.4  | 693.17  | 563.19  |

| V0          | 0.2  | 714.019 | 594.07  |

| la S        | 0    | 733.83  | 621.96  |

| y b         | -1   | 821.67  | 733.83  |

| Body bias   | -0.8 | 805.3   | 714.09  |

| m           | -0.6 | 788.4   | 693.2   |

|             | -0.4 | 770.907 | 671.08  |

|             | -0.2 | 752.75  | 647.46  |

|             | 0    | 733.83  | 621.96  |

Threshold voltage(V)

Fig. 2 Impact of body biasing voltage on Threshold voltage of access transistor

and NM5 decreases by 15.24% and 18.30% respectively for the bias voltage variation from 0 to 1V while threshold voltage increases by 11.97% and 17.99% respectively for NM4 and NM5 for reverse body voltage variation from 0 to -1 V.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) 2923 © Copyright: All rights reserved.

## Reverse body biasing of NMOS

The substrate of PMOS transistor is coupled to supply voltage and substrate of NMOS transistor is decreased beyond ground voltage, it indicates the reverse body biasing of NMOS.

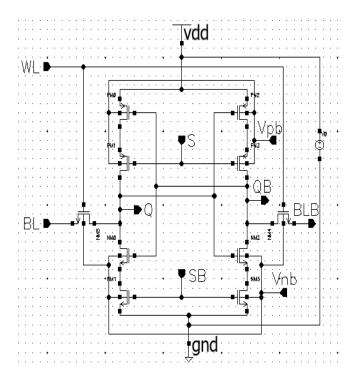

The simulation result of impact of reverse body bias of NMOS on transient power, delay and energy (power delay product-PDP) is shown in Fig.3. It can be observed that transient power is increasing but it is less prominent to the reduction of delay, resulting in the reduction of energy as

Fig.3 Impact of RBB voltage on delay, transient power and PDP

RBB voltage reduces from 0 to -1 V. The transient power is increases by 3.22% while the delay and energy consumption decrease by 84.56 % and 84.06 % respectively.

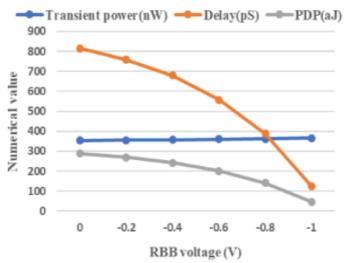

The effect of RBB voltage on leakage power at 1 V of supply is seen in the Fig.4. It reduces by 30.62 % for variation of RBB voltage from 0 to -1 V.

Fig.4 Impact of RBB on leakage power

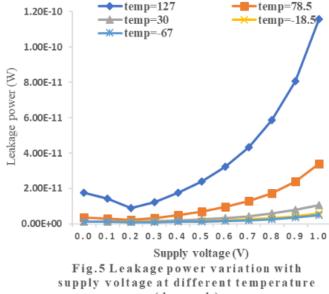

Fig.5 illustrates the parametric analysis of leakage power with variation of supply voltage from 0 to 1 V at different temperature ranging between -67 °C to 127 °C.

(deg. cel.)

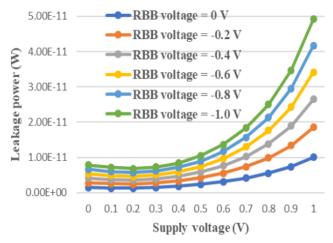

The leakage power trend with variation of supply voltage at different RBB voltage at 27 °C temperature can be observed from Fig.6. The leakage power is maximum for -1 V of body biasing voltage and minimum for zero body

Fig.6 Effect of supply voltage on leakage power at differrnt RBB voltage

biasing voltage. For lesser value of voltage, the leakage power is less but it increases exponentially after 0.5 V of voltage.

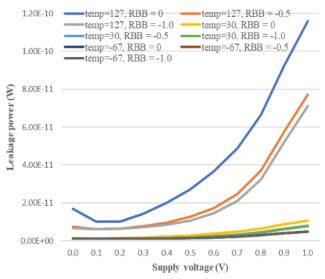

The combined outcome of temperature and RBB voltage on leakage power with variation of supply voltage is observed in Fig.7. The leakage power is maximum for condition of 127°C and 0 RBB voltage followed by same temperature with -0.5 V and -1.0 V respectively.

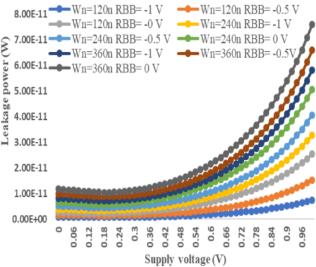

The simulation work is also carried out to examine the collective impact of variation of access transistor width and RBB voltage at distinct supply voltage as shown in Fig.8. It is seen that the leakage power is least for the access transistor width of 120 n and -1 V of RBB voltage and maximum for 360 n width and 0 V RBB voltage. The analysis depicts that the leakage power increases with increase of width and decrease of RBB voltage.

## Consequences of Body-Biasing Technique on SRAM Memory

Fig. 7 Impact of both temperature (degree celcius) and RBB voltage (V) on leakage power

Fig.8 Impact of supply voltage on leakage power with different access transistor width and RBB voltage

#### IV. CONCLUSION

This paper investigates the consequences of body biasing technique implemented on NMOS transistor of 10T SRAM memory cell. The forward and reverse body biasing approach is implemented on the access transistor of memory to examine affect on threshold voltage. Reverse body biasing is imposed on NMOS and the PMOS body remains at the source potential. The reverse biasing varied from 0 to -1 V at room temperature and observed that it has dominant effects on reduction of leakage power, delay, and PDP while a marginal increase of transient power is also observed. The impact of source voltage variation on leakage power with different RBB voltage, temperature and both are detected. It is seen that the leakage power decreases with decrease of temperature and increase of RBB voltage. The leakage power trend for width of access transistors along with biasing voltage are observed for different supply voltage. It is concluded that as width of transistor increases with RBB voltage, the leakage power increases.

Retrieval Number: I8637078919/19©BEIESP DOI: 10.35940/ijitee.I8637.0881019 Journal Website: www.ijitee.org

#### REFERENCES

- A.P. Shah, N. Yadav, A. Beohar, S.K Vishvakarma, "On-chip Adaptive Body Bias for Reducing the Impact of NBTI on 6T SRAM Cells," IEEE Transactions on Semiconductor Manufacturing. Vol. 31, pp.1–8, 2018.

- M. Kumar, J.S. Ubhi, "Performance evaluation of 6T, 7T & 8T SRAM at 180 nm technology" 8th International Conference on Computing, Communications and Networking Technologies (ICCCNT), pp. 1-6

- Y. Wang, M. Enachescu, S.D. Cotofana, L. Fang, "Microelectronics Reliability Variation tolerant on-chip degradation sensors for dynamic reliability management systems," Microelectronics Reliability, vol. 52, pp. 1787-1791, 2012.

- Neil H.E. Weste, and Kamran Eshraghian. "Principles of CMOS VLSI design: a systems perspective," Pearson Education, second edition, pp. 51-52,2004.

- S. Narendra, A. Keshavarzi, A. B. Bloechel, S. Borkar, & V. De, "Forward body bias for microprocessors in 130-nm technology generation and beyond," IEEE Journal of Solid-State Circuits, vol. 38 no. 5, pp. 696-701, 2003.

- W. James Tschanz, Siva Narendra, Raj Nair, and Vivek De, "Effectiveness of adaptive supply voltage and body bias for reducing impact of parameter variations in low power and high performance microprocessors," IEEE Journal of Solid-State Circuits, vol. no. 5 pp. 826-829, 2003.

- C. Wann, J. Harrington, R. Mih, S. Biesemans, K. Han, R. Dennard, O. Prigge, C. Lin, R. Mahnkopf and B. Chen, "CMOS with active well bias for low-power and RF/analog applications," IEEE Symposium on VLSI Technology. Digest of Technical Papers (Cat. No. 00CH37104), pp. 158-159, June 2000.

- N. Kimizuka, Y. Yasuda, T. Iwamoto, I. Yamamoto, K. Tanaka, Y. Akiyama, and K. Imai, "Ultralow standby power (U-LSTP) 65-nm node CMOS technology utilizing HfSiON dielectric and body-biasing scheme," in VLSI Symp. Tech. Dig., pp. 218-219, 2005.

- S.F. Huang, C. Wann, Y.S. Huang, C.Y. Lin, T. Schafbauer, S.M. Cheng, Y.C. Cheng, D. Vietzke, M. Eller, C. Lin, and Q. Ye, "Scalability and biasing strategy for CMOS with active well bias". In IEEE Symposium on VLSI Technology, Digest of Technical Papers pp. 107-108, June 2001.

- A. Keshavarzi, S. Narendra, S. Borkar, C. Hawkins, K. Royi, & V. De, "Technology scaling behavior of optimum reverse body bias for standby leakage power reduction in CMOS IC's," In IEEE Proceedings, International Symposium on Low Power Electronics and Design, pp. 252-254, August 1999.

- V. Kursun, & E. G. Friedman, "Multi-voltage CMOS circuit design," John Wiley & Sons pp. 169-169.

#### **AUTHORS PROFILE**

Mukesh Kumar received the B.Tech. degree from West Bengal university, Kolkata and M.Tech. degree from Sant Longowal Institute of Engineering and Technology, Longowal (Punjab) in 2011 and 2014 respectively. He is currently pursuing Ph.D. degree in the Department of Electronic and Communication, Sant

Longowal Institute of Engineering and Technology, Longowal (Punjab). His current research interests include Image processing, low power VLSI design, and Radiation hardened memory design. He is reviewer of SCI and other peer reviewed journals and has 1 year of teaching as well as 4 years of Research experience

Jagpal Singh Ubhi received the B. E. degree and M.E. degree from Thapar Institute of Engineering & Technology, Patiala (Punjab) in 1994 and 2000 respectively. He received his Ph. D. degree from Punjab Technical University, Jalandhar in 2011. He is now working as a Professor at Sant Longowal Institute of

Engineering and Technology, Longowal. He is in teaching profession for the last 24 years. His current research interests include digital communication theory, wireless fading channels, diversity systems, wireless digital communications and VLSI design. He is life member of IE(India), IETE(India), IAENG and member of IEEE.